KS3 Theory Topics Resources (14-16 years)

- An editable PowerPoint lesson presentation

- Editable revision handouts

- A glossary which covers the key terminologies of the module

- Topic mindmaps for visualising the key concepts

- Printable flashcards to help students engage active recall and confidence-based repetition

- A quiz with accompanying answer key to test knowledge and understanding of the module

A-Level Types Of Processor (16-18 years)

- An editable PowerPoint lesson presentation

- Editable revision handouts

- A glossary which covers the key terminologies of the module

- Topic mindmaps for visualising the key concepts

- Printable flashcards to help students engage active recall and confidence-based repetition

- A quiz with accompanying answer key to test knowledge and understanding of the module

The general definition of a processor or a microprocessor is: A small chip that is placed inside the computer as well as other electronic devices.

In very simple terms, the main job of a processor is to receive input and then provide the appropriate output (depending on the input).

Modern-day processors have become so advanced that they can handle trillions of calculations per second, increasing efficiency and performance.

Both RISC and CISC architectures have been developed largely as a breakthrough to cover the semantic gap. The semantic gap, is the gap that is present between machine language and high-level language.

Therefore the main objective of creating these two architectures is to improve the efficiency of software development, and by doing so, there have been several programming languages that have been developed as a result, such as Ada, C++, C, and Java etc.

These programming languages provide a high level of power and abstraction.

Therefore to allow for efficient compilation of these high-level language programs, RISC and CISC are used.

What are RISC processors?

Reduced Instruction Set Computer (RISC), is a type of computer architecture that operates on a small, highly optimised set of instructions, instead of a more specialised set of instructions, which can be found in other types of architectures. This architecture means that the computer microprocessor will have fewer cycles per instruction.

The word “Reduced Instruction Set” may be incorrectly interpreted to refer to “reduced number of instructions”. Though this is not the case, the term actually means that the amount of work done by each instruction is decreased in terms of the number of cycles.

Due to the design of Alan Turing 1946 Automatic Computing Engine, it had many characteristics that resembled RISC architecture, furthermore many traits of RISC architectures were seen in the 1960s due to them embodying the load/store approach.

That being said the term RISC had first been used by David Patterson of “Berkeley RISC project”, who is considered to be a pioneer in his RISC processor designs. Patterson is currently the Vice-Chair of the Board of Directors of the RISC-V Foundation.

A RISC chip doesn’t require many transistors, which makes them less costly to design and produce. One of RISCs main characteristics is that the instruction set contains relatively simple and basic instructions from which more complex instructions can be produced.

RISC processors/architectures are used across a wide range of platforms nowadays, ranging from tablet computers to smartphones, as well as supercomputers (i.e. Summit top500 list in 2018).

The characteristics of RISC processors

Some the terminology which can be handy to understand:

- LOAD: Moves data from the memory bank to a register.

- PROD: Finds product of two operands located within the register.

- STORE: Moves data from a register to the memory banks.

Addressing modes: An addressing mode is an aspect of instruction set architecture in most CPU designs.

- The RISC architecture utilises simple instructions.

- RISC synthesises complex data types and supports few simple data types.

- RISC makes use of simple addressing modes and fixed length instructions for pipelining.

- RISC allows any register to be used in any context.

- RISC has only one cycle for execution time.

- The work load of a computer that has to be performed is reduced by operating the “LOAD” and “STORE” instructions.

- RISC prevents various interactions with memory, it does this by have a large number of registers.

- Pipelining in RISC is carried out relatively simply. This is due to the execution of instructions being done in a uniform interval of time (i.e. one click).

- More RAM is required to store assembly level instructions.

- Reduced instructions need a smaller number of transistors in RISC.

- RISC utilises the Harvard architecture

- To execute the conversion operation, a compiler is used. This allows the conversion of high-level language statements into code of its form.

- RISC processors utilise pipelining.

- Pipelining is a process that involves improving the performance of the CPU. The process is completed by fetching, decoding, and executing cycles of three separate instructions at the same time.

A RISC architecture system contains a small core logic processor, which enables engineers to increase the register set and increase internal parallelism by using the following techniques:

Thread Level Parallelism:

Thread level parallelism increases the number of parallel threads executed by the CPU.

Thread level parallelism can also be identified as “Task Parallelism”, which is a form of parallel computing for multiple computer processors, using a technique for distributing the execution of processes and threads across different parallel processor nodes. This type of parallelism is mostly used in multitasking operating systems, as well as applications that depend on processes and threads.

Instruction Level Parallelism:

Instructions level parallelism increases the speed of the CPU in executing instructions. This type of parallelism that measures how many of the instructions in a computer can be executed simultaneously.

However, Instruction level parallelism is not to be confused with concurrency. Instruction level parallelism is about the parallel election of a sequence of instructions, which belong to a specific thread of execution of a process.

Whereas concurrency is about threads of one or different processes being assigned by the CPU’s core in a mannered and strict alteration or in true parallelism (provided that there are enough CPU cores).

Advantages of RISC processors

- Due to the architecture having a set of instructions, this allows high level language compilers to produce more efficient code.

- This RISC architecture allows simplicity, which therefore means that it allows developers the freedom to utilise the space on the microprocessor.

- RISC processors make use of the registers to pass arguments and to hold local variables.

- RISC makes use of only a few parameters, furthermore RISC processors cannot call instructions, and therefore, use a fixed length instruction, which is easy to pipeline.

- Using RISC, allows the execution time to be minimised, whilst increasing the speed of the overall operation, maximising efficiency.

- As mentioned above, RISC is relatively simple, this is due to having very few instructional formats, and a small number of instructions and a few addressing modes required.

Disadvantages of RISC processors

- The performance of RISC processors depends on the compiler or the programmer. The following instructions might rely on the previous instruction to finish their execution.

- RISC processors require very fast memory systems to feed various instructions, thus a large memory cache is required.

What are CISC processors?

CISC, which stands for “Complex Instruction Set Computer”, is a computer architecture where single instructions can execute several low-level operations, for instance, “load from memory an arithmetic operation, and a memory store). CISC processors are also capable of executing multi-step operations or addressing modes with single instructions.

CISC, as with RISC, is a type of microprocessor that contains specialised simple/complex instructions.

Until recent times, all major manufacturers of microprocessors had used CISC based designs to develop their products. The reason for that was because, CISC was introduced around the early 1970s, where it was used for simple electronic platforms, such as stereos, calculators, video games, not personal computers, therefore allowing the CISC technology to be used for these types of applications, as it was more suitable.

However, eventually, CISC microprocessors found their way into personal computers, this was to meet the increasing need of PC users. CISC manufacturers started to focus their efforts from general-purpose designs to a high-performance computing orientation.

Advantageously, CISC processors helped in simplifying the code and making it shorter in order to reduce the memory requirements.

In CISC processors, every single instruction has several low-level operations. Yes, this makes CISC instructions short, but complex.

Some examples of CISC processors are:

- IBM 370/168 and Intel 80486

- Also non-trivial items such as government databases were built using a CISC processor

The characteristics of CISC processors

As mentioned above, the main objective of CISC processors is to minimise the program size by decreasing the number of instructions in a program.

However, to do this, CISC has to embed some of the low-level instructions in a single complex instruction. Moreover, this means that when it is decoded, this instruction generates several microinstructions to execute.

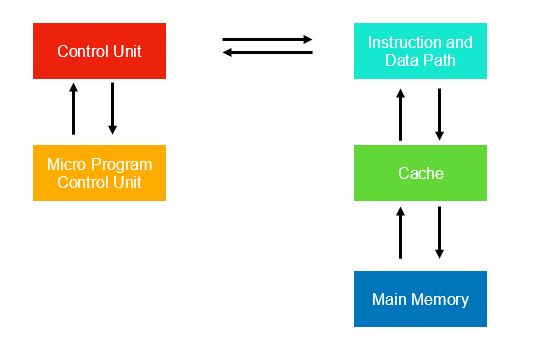

The complex architecture of CISC is below:

Microprogram Control Unit:

The microprogram control unit uses a series of microinstructions of the microprogram stored in the “control memory” of the microprogram control unit and generate control signals.

Control Unit:

The control units access the control signals, which are produced by the microprogram control unit, moreover, they operate the functioning of processors hardware.

Instructions and data path:

The instructions and the data path retrieve/fetches the opcode and operands of the instructions from the memory.

Cache and main memory:

This is the location where the program instructors and operands are stored.

Instructions in CISC are complex, and they occupy more than a single word in memory. Like we saw in RISC, CISC also uses LOAD/STORE to access the memory operands, however, CISC also has a “MOVE” instruction attribute, which is used to gain access to memory operands.

Though one advantageous characteristic of the “MOVE” operation, is that it has a wider scope. This allows the CISC instructions to directly access memory operands.

CISC instruction sets also have additional addressing modes:

- Auto-increment mode:

- The address of an operand is the content of the register. It is automatically incremented after accessing the registers content, in order to point to the memory location of the next operand.

- Auto-decrement mode:

- Like “auto-increment”, the address of an operand is the content of the register. However with auto-decrement, initially the contest of register is decremented, moreover then the content of the register is used as an address for an operand.

- Relative Mode:

- The program counter is used instead of a general-purpose register. This allows to refer large range of area in memory.

Advantages of CISC processors

- Memory requirement is minimised due to code size.

- The execution of a single instruction will also execute and complete several low level tasks.

- Memory access is more flexible due to the complex addressing mode.

- Memory locations can be directly accessed by CISC instructions.

- Microprogramming is easy to implement and less expensive than wiring a control unit.

- If new commands are to be added to the chip, the structure of the instruction set does not need to be changed. This is because the CISC architecture uses general purpose hardware to carry out commands.

- The compiler doesn’t have to be complicated, as the microprogram instruction sets can be written to match the high-level language constructs.

Disadvantages of CISC processors

- Although the code size is minimised, the code requires several clock cycles to execute a single instruction. Therefore decreasing the efficiency of the system.

- The implementation of pipelining in CISC is regarded to be complicated.

- In order to simplify the software, the hardware structure needs to be more complex.

- CISC was designed to minimise the memory requirement when memory was smaller and more expensive. However nowadays memory is inexpensive and the majority of new computer systems have a large amount of memory, compared to the 1970’s when CISC first emerged.

RISC vs. CISC

| RISC | CISC |

| RISC focuses on software | CISC focuses on hardware |

| Single clock, reduced instruction only, which means the instructions are simple compared to CISC | Multi-clock complex instructions |

| Operates on Register to Register. However, “LOAD” and “STORE” are independent instructions | CISC operates from Memory to Memory: The “LOAD” and “STORE” are incorporated in instructions. Also uses MOVE |

| RISC has large code sizes, which means it operates low cycles per second | CISC has small code sizes, high cycles per second |

| Spends more transistors on memory registers | The transistors in a CISC processor are used to store complex instructions |

| Less memory access | More memory access |

| Implementing pipelining on RISC is easier | Due to CISC instructions being of variable length, and having multiple operands, as well as complex addressing modes and complex instructions this increases complexity. Furthermore, CISC as defined above occupies more than a memory word. Thus taking several cycles to execute operand fetch. Implementing pipelining on CISC is complicated |

Although the above showcases differences between the two architectures, the main difference between RISC and CISC is the CPU time taken to execute a given program.

CPU execution time is calculated using this formula:

CPU time = (number of instruction) x (average cycles per instruction) x (seconds per cycle)

RISC architectures will shorten the execution time by reducing the average clock cycle per one instruction.

However, CISC architectures try to reduce execution time by reducing the number of instructions per program.

Summary and Facts

A reduced Instruction Set Computer (RISC), can be considered as an evolution of the alternative to Complex Instruction Set Computing (CISC). With RISC, in simple terms, its function is to have simple instructions that do less but execute very quickly to provide better performance.

What are RISC processors?

- Reduced Instruction Set Computer (RISC), is a type of computer architecture which operates on small, highly optimised set of instructions, instead of a more specialised set of instructions, which can be found in other types of architectures. This architecture means that the computer microprocessor will have fewer cycles per instruction.

- RISC processors/architectures are used across a wide range of platforms nowadays, ranging from tablet computers to smartphones, as well as supercomputers

- Thread Level Parallelism:

- Thread level parallelism increases the number of parallel threads executed by the CPU.

- Instruction Level Parallelism:

- Instructions level parallelism increases the speed of the CPU’s executing instructions.

Advantages and Disadvantages of RISC processors

Advantages:

- Greater performance due to simplified instruction set

- Uses pipelining efficiently

- RISC can be easily designed in compared to CISC

- Less expensive, as they use smaller chips

Disadvantages:

- Performance of the processor will depend on the code being executed

- RISC processors require very fast memory systems to feed different instructions. This requires a large memory cache.

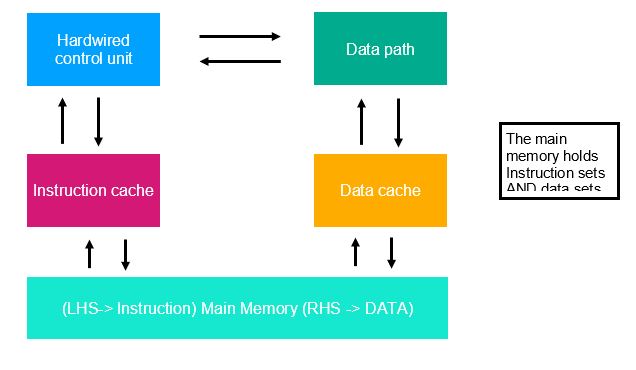

The characteristics of RISC processor structure:

- Hardwired Control Unit

- Data Path

- Instruction Cache

- Data Cache

- Main Memory

- Only Load and store instructions have access to memory

- Fewer number of addressing modes

- RISC includes a less complex pipelining architecture compared to CISC

What are CISC processors?

- CISC, which stands for “Complex Instruction Set Computer”, is computer architecture where single instructions can execute several low level operations. CISC processors are also capable of executing multi-step operations or addressing modes with single instructions.

- CISC, as with RISC, is a type of microprocessor that contains specialised simple/complex instructions.

- The primary objective for CISC processors is to complete a task in as few lines of assembly as possible. To accomplish this, processor hardware must be built able to comprehend and execute a series of operations.

Advantages and disadvantages of CISC processors:

Advantages:

- Allows for simple small scripts

- Using CISC, complex commands are readable

- Most code is built to be implemented on CISC

Disadvantages:

- CISC processors are larger as they contain more transistors

- May take multiple cycles per line of code, decreasing efficiency

- Lower clock speed

- Complex use of pipelining

- Compared to RISC, they are more complex, which means they are more expensive

The characteristics of CISC processor structure:

- Microprogram Control Unit

- Control Unit

- Instructions and data path

- Cache and main memory

CISC instruction sets also have additional addressing modes:

- Auto-increment mode

- Auto-decrement mode

- Relative Mode

- CISC uses STORE/LOAD/MOVE

References:

- https://techterms.com/definition/processor

- https://cs.stanford.edu/people/eroberts/courses/soco/projects/risc/whatis/index.html

- https://en.wikipedia.org/wiki/David_Patterson_(computer_scientist)

- https://cs.stanford.edu/people/eroberts/courses/soco/projects/risc/risccisc/

- https://en.wikipedia.org/wiki/Instruction-level_parallelism

- https://simple.wikipedia.org/wiki/Task_parallelism#:~:text=Task%20parallelism%20(also%20known%20as,across%20different%20parallel%20processor%20nodes.

- https://www.studytonight.com/computer-architecture/risc-cisc-processors

- https://www.techopedia.com/definition/2887/reduced-instruction-set-computer-risc

- https://www.watelectronics.com/what-is-risc-and-cisc-architecture/

- https://www.quora.com/What-are-the-advantages-and-disadvantages-of-RISC-microprocessors

- http://www.borrett.id.au/computing/art-1991-06-02.htm#:~:text=History%20of%20RISC%20and%20CISC,microprocessors%20used%20CISC%20based%20designs.

- https://en.wikipedia.org/wiki/Addressing_mode

- https://en.wikipedia.org/wiki/Complex_instruction_set_computer#Historical_design_context

- https://techterms.com/definition/cisc

- https://getrevising.co.uk/grids/cisc

- https://binaryterms.com/cisc-processors.html#AdvantagesandDisadvantages

- https://www.electronicshub.org/risc-and-cisc-architectures/#:~:text=Disadvantages%20of%20CISC%20Architecture,-A%20new%20or&text=Therefore%2C%20chip%20hardware%20and%20instruction,design%20to%20perform%20many%20functions.